三星电子正遭遇重大挑战,尤其是在半导体业务方面。除了代工业务停滞不前外,其在高带宽存储器(HBM)领域的竞争力也令人担忧。业内消息称,三星可能会重新设计部分1a DRAM电路,以增强其HBM竞争力。

据报道,三星最初计划在2024年第三季度开始向英伟达供应HBM3E。然而,其8层产品尚未通过质量测试,12层产品可能会推迟到2025年第二或第三季度。

专家认为,三星无法通过测试的主要原因是其DRAM存在问题。由于高带宽存储器(HBM)垂直堆叠多个DRAM芯片,其性能在很大程度上取决于底层DRAM技术。

2020年,三星成为首家在DRAM制造中引入EUV(极紫外)技术的公司。然而,一些分析师猜测,三星HBM3E面临的竞争力挑战可能与1a DRAM关键组件有关。10nm级DRAM经历了从1x、1y和1z到1a、1b的迭代。三星于2021年下半年开始量产1a DRAM,在五层中采用了EUV技术,而其竞争对手SK海力士仅在一层中采用了EUV。

然而,这种方法似乎没有达到预期。在DRAM生产中使用EUV降低了大规模生产过程中的工艺稳定性,从而无法实现预期的成本降低。

此外,三星的DRAM(尤其是用于服务器的DRAM)设计似乎并不是最理想的,这也是该公司在这一应用领域推出DDR5的时间晚于竞争对手的原因之一。2023年1月,SK海力士率先获得英特尔认证,并推出了基于其1a DRAM的服务器DDR5产品。

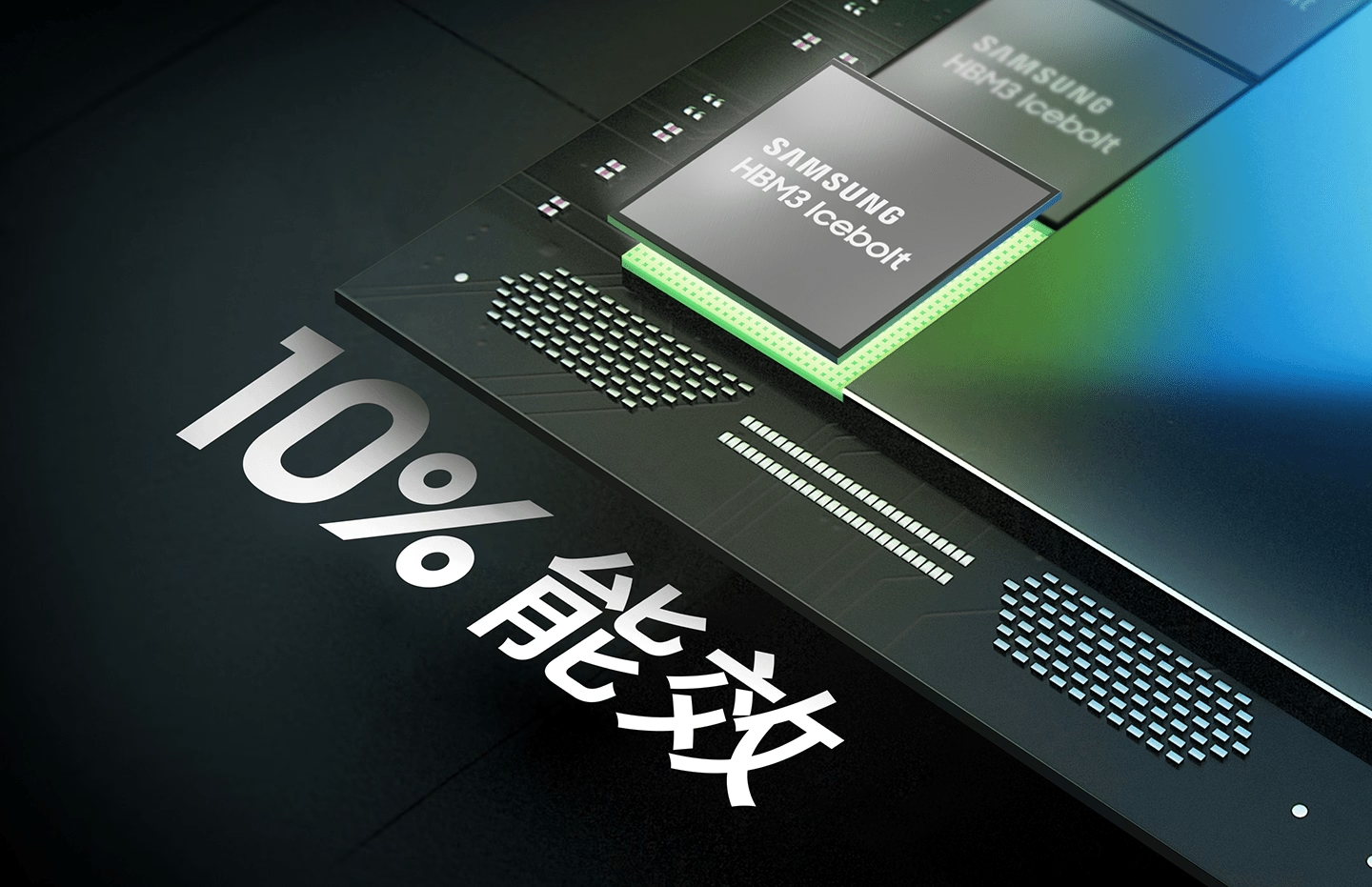

三星推迟为英伟达量产HBM3E引发了有关重新设计其1a DRAM的讨论。报告显示,三星的8层HBM3E的数据处理速度比SK海力士和美光的产品低约10%。

据报道,为了在服务器DRAM和HBM领域恢复竞争力,三星正在考虑进行战略调整,以改进其DRAM产品。尽管尚未做出最终决定,但有关重新设计部分1a DRAM电路的内部讨论仍在进行之中,这种方法存在重大风险。

近日,三星设备解决方案(DS)部门主管Jun Young-hyun在公布公司2023年第三季度初步业绩时罕见地作出道歉,因为该业绩低于市场预期。他强调,管理层应承担全部责任,领导团队将采取行动克服危机,重新崛起。

三星能否通过HBM3E质量认证或放弃该项目,可能取决于其重新设计部分1a DRAM电路的决定。如果进行重新设计,可能至少需要6个月的时间,最早可能在2025年第二季度开始量产。不过,即使重新设计工作进展顺利,考虑到当前的市场条件,确保及时供应产品仍将是一项挑战。(校对/张杰)